第一章 数字逻辑基础

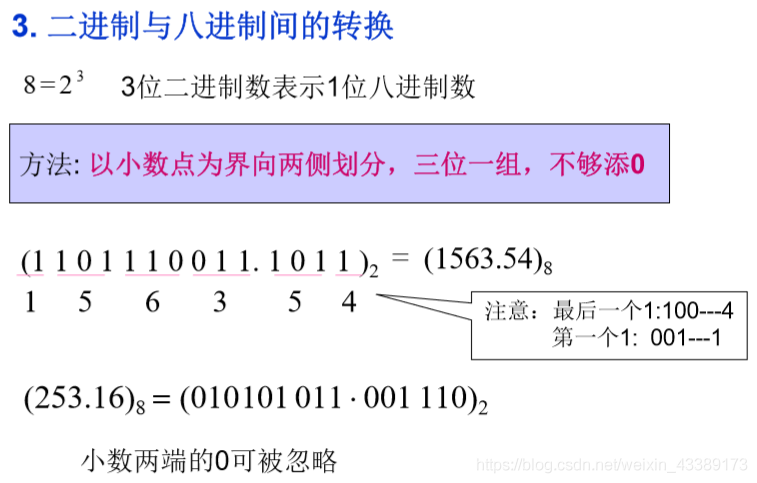

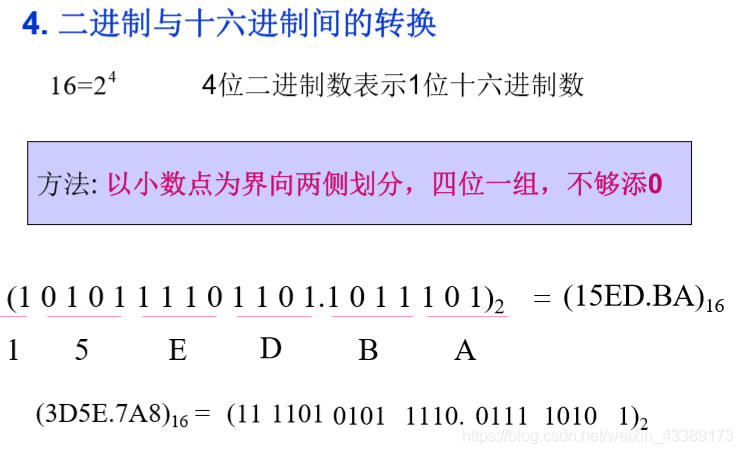

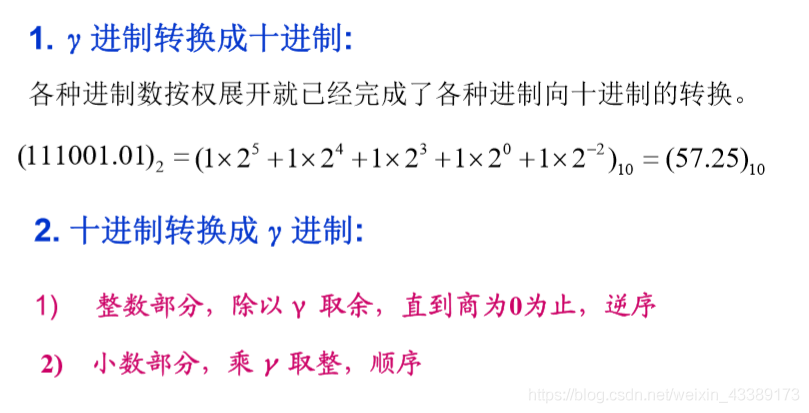

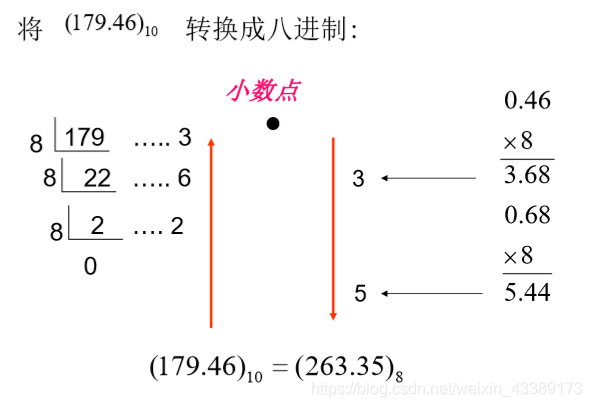

二进制、八进制、十进制和十六进制之间的转换

- 十进制和二进制、八进制、十六进制相互转换

- 例1.

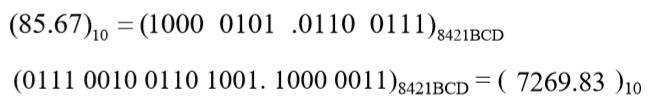

8421BCD码与十进制之间的转换

例1.

十进制与原码、反码、补码之间的转换

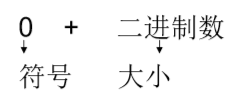

- 正数

- 原码

- 反码、补码与原码相同

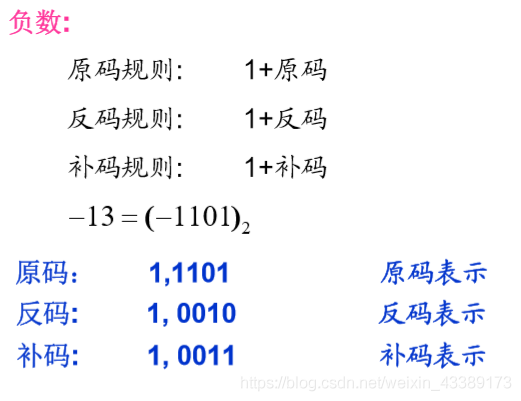

- 负数

- 原码:符号位为1+对应二进制数

- 反码:原码符号位不变,其余取反

- 补码:反码最低有效位加1

第二章 逻辑门电路

逻辑门

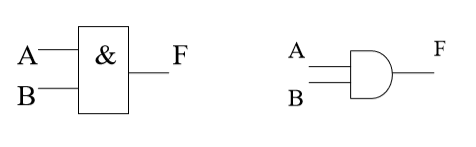

- 与门

- 符号

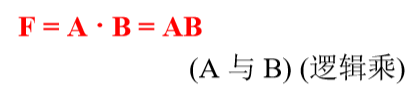

- 表达式

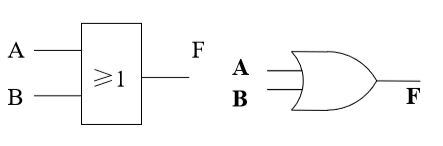

- 或门

- 符号

- 表达式:F=A+B

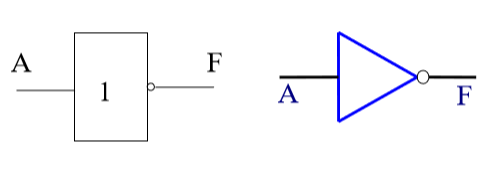

- 非门

- 符号

- 表达式

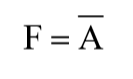

- 复合逻辑门

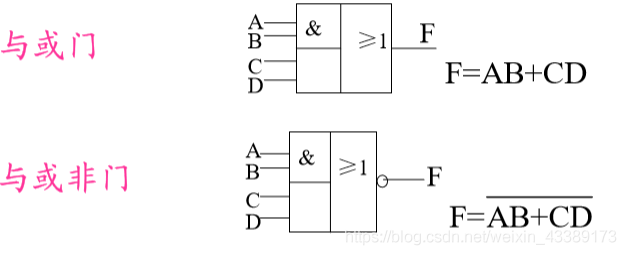

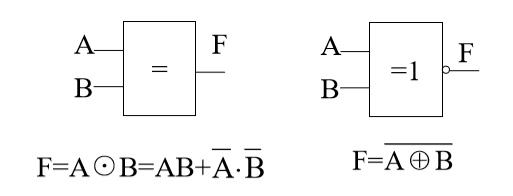

- 异或门

- 同或门

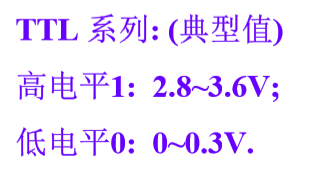

TTL与非门

- 电压传输特性

- 输入/输出特性

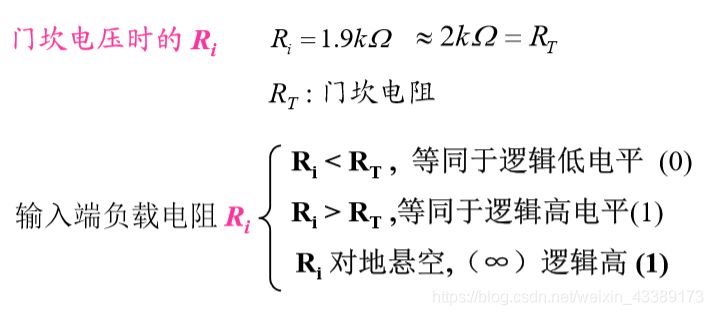

- 例题:

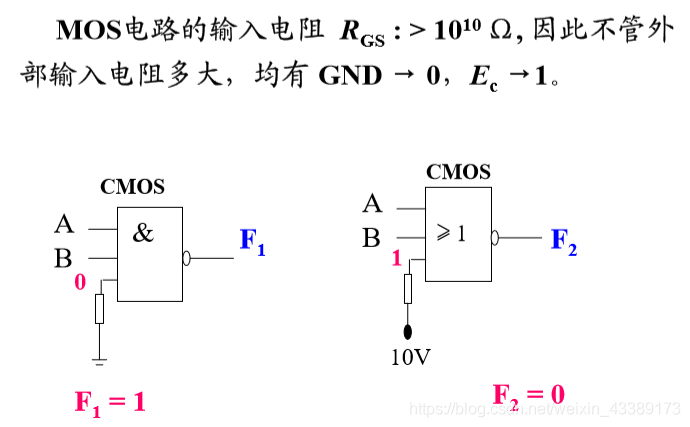

MOS逻辑电路

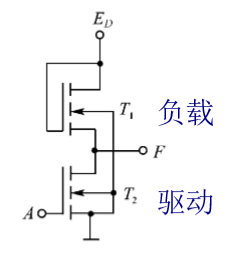

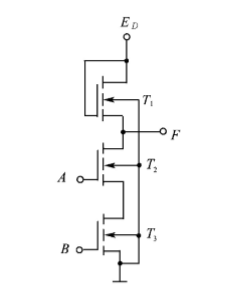

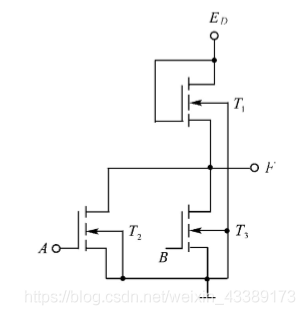

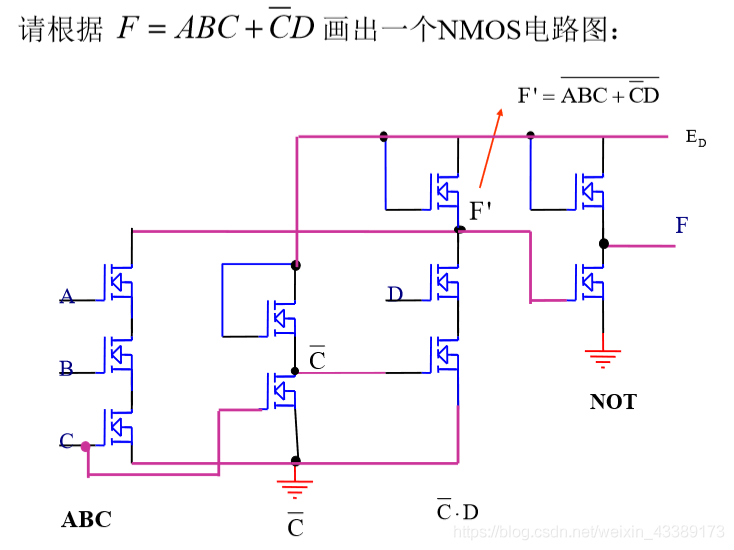

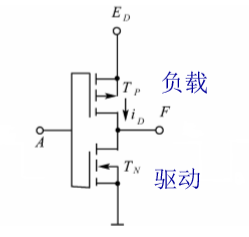

- NMOS门电路

- 非门

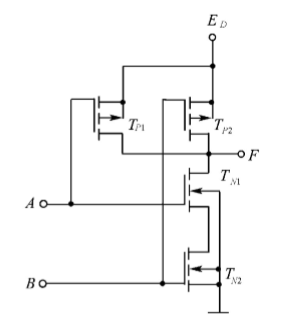

- 与非门

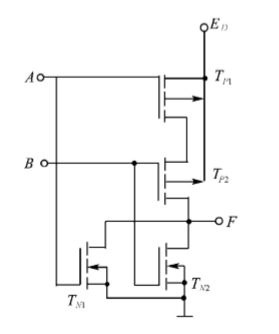

- 或非门

- 例题:

- CMOS门电路

- 非门

- 与非门

- 或非门

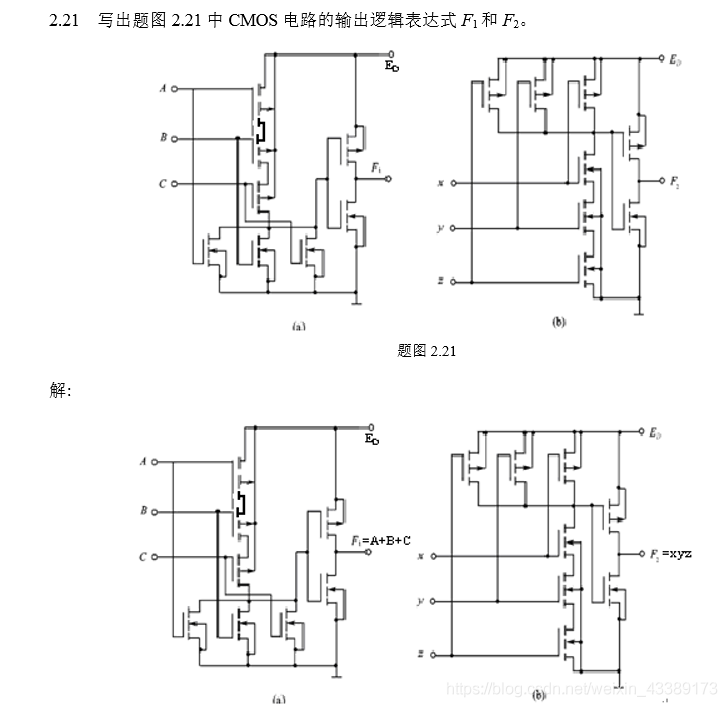

- 例题1:

- 例题 2:

第三章 逻辑代数

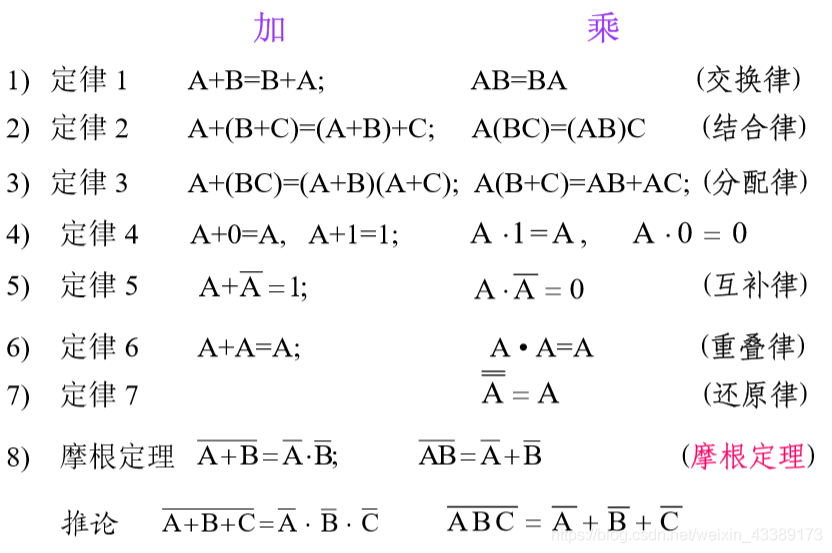

逻辑代数运算法则

- 逻辑代数的基本定律

- 基本规则

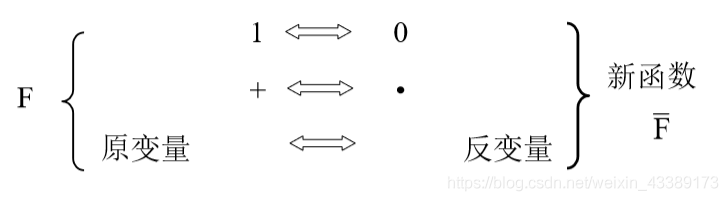

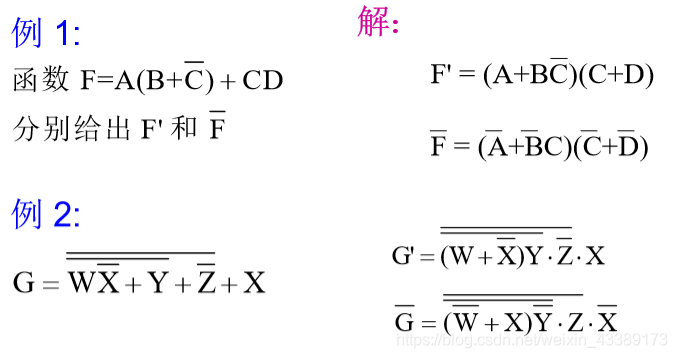

- 反演规则

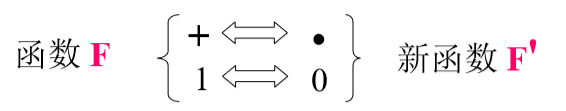

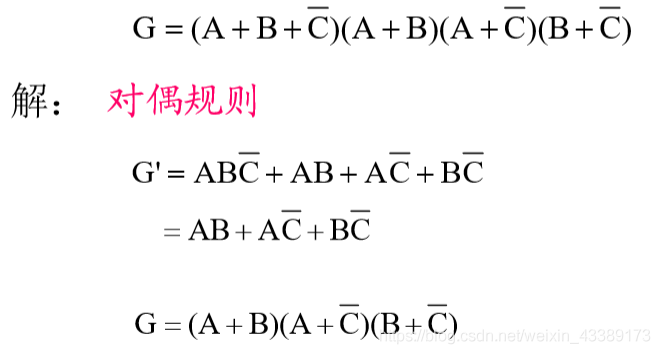

- 对偶规则

- 例题:

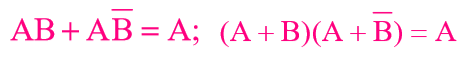

- 常用公式

逻辑函数标准形式

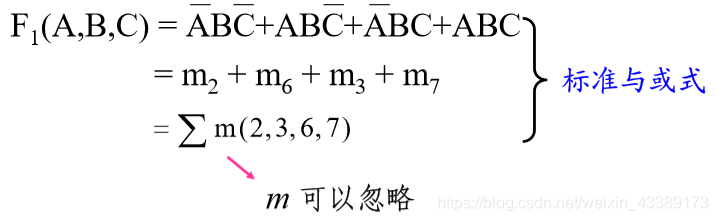

- 最小项及标准与或式

- m表示。1:原变量,0:反变量

- 任意两最小项之积为0

- 全体最小项之和为1

- 标准与或式

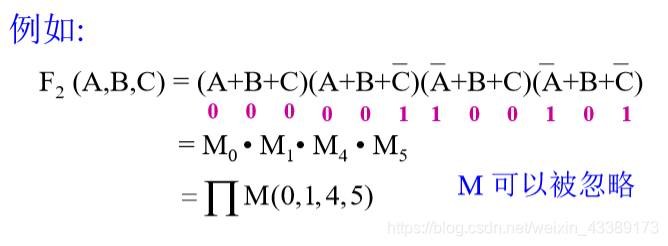

- 最大项及标准或与式

- M表示。0:原变量,1:反变量

- 任意两最大项之和为1

- 全体最大项之积为0

- 标准或与式

- 两种标准式间的关系

- 最大项与最小项互为反函数

- 如果不在最小项中出现的编码,一定出现在最大项的编号中。

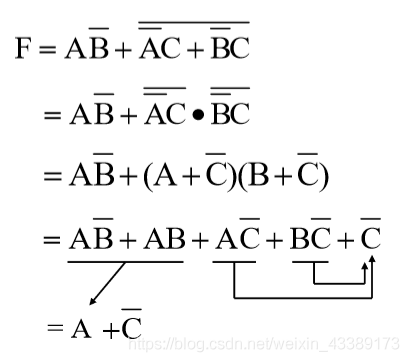

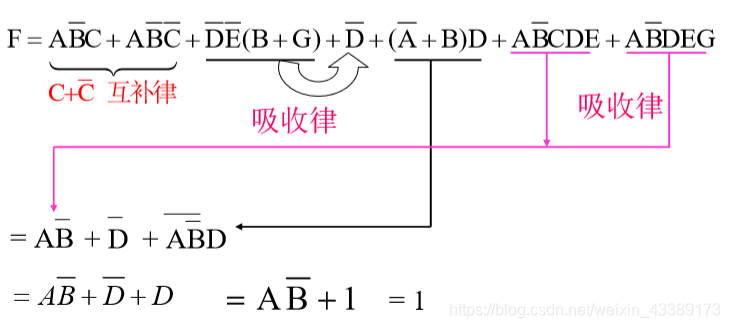

逻辑函数的公式化简法

- 例1:

- 例2:

- 例3:

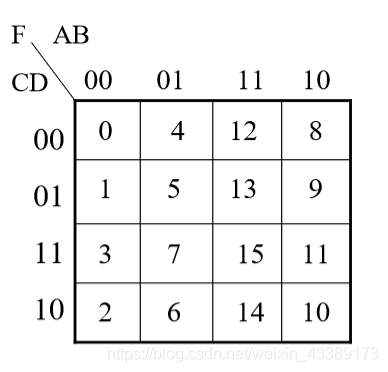

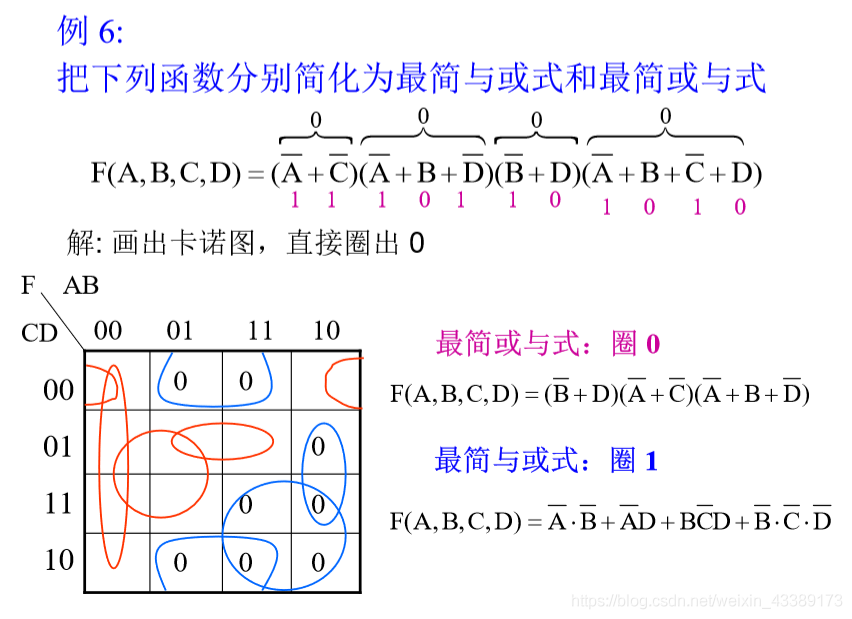

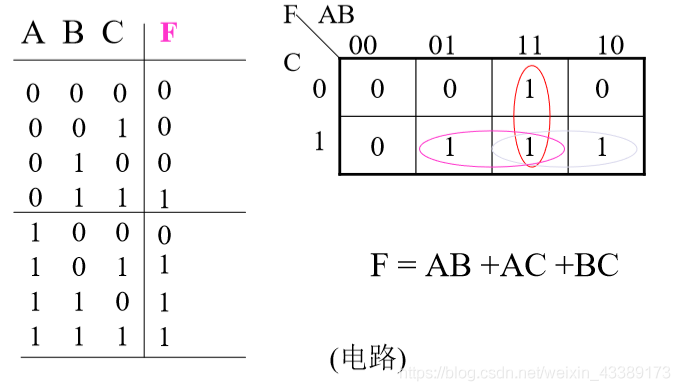

逻辑函数的卡诺图化简法

- 4个变量的卡诺图

- 最小项时,F为1;最大项时,F为0

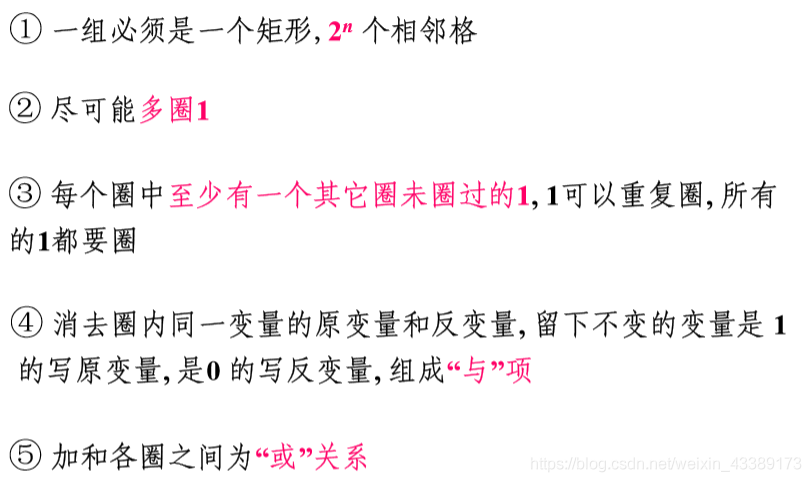

- 求最简与或式

- 方法:圈相邻格中的1, 合并最小项

- 根据下面规则将含有 1 的相邻格圈在一起:

- 例:

- 求最简或与式(圈0)

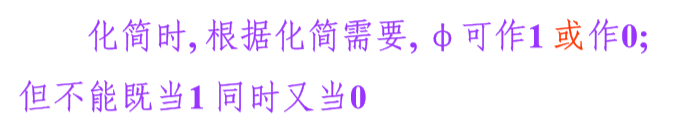

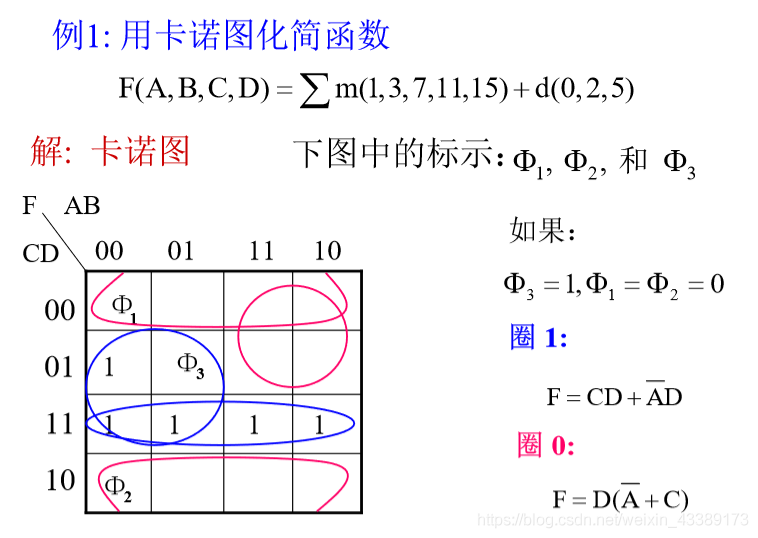

- 具有随意项的逻辑函数的化简

- 例:

第四章 组合逻辑电路

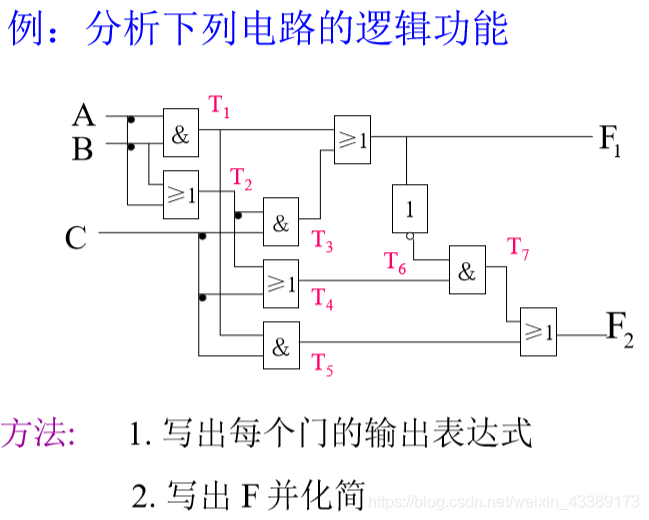

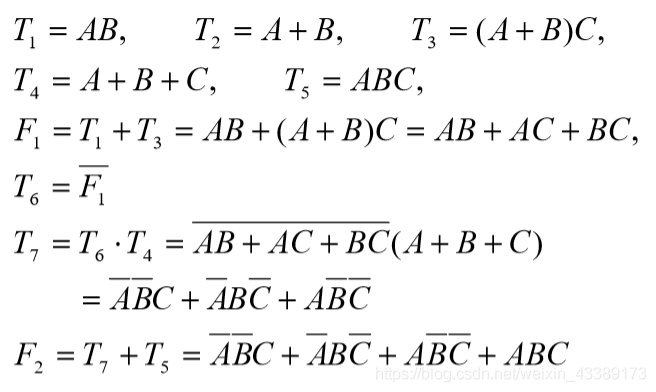

组合逻辑电路分析

- 步骤

- 根据输入逐级写出输出内容

- 化简逻辑功能

- 列出真值表

- 讨论功能

- 例题:

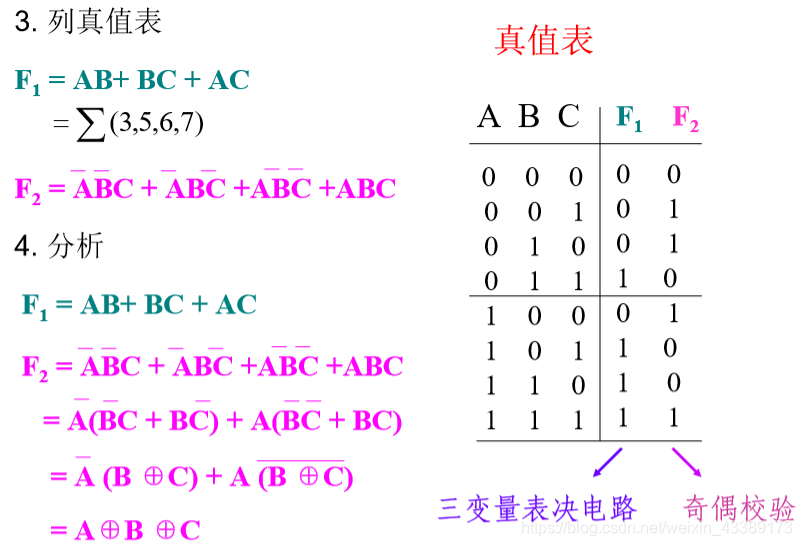

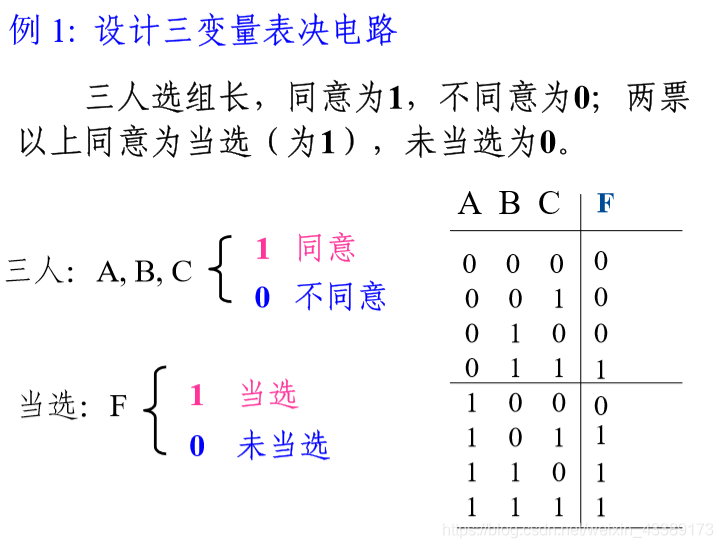

组合逻辑电路设计

- 步骤

- 确定输入、输出以及它们之间的关系

- 列出真值表

- 化简

- 画出逻辑电路图

- 例题:

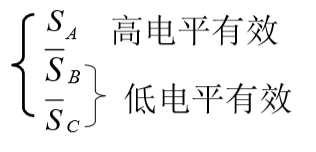

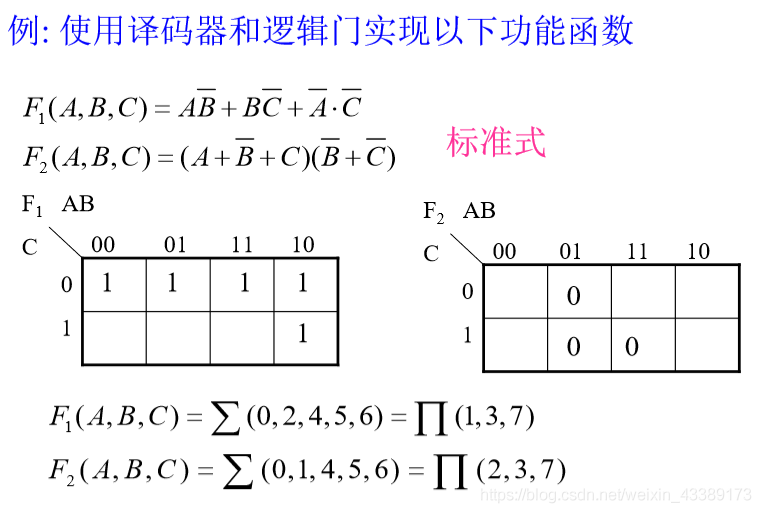

译码器

- 二进制译码器

- 低电平有效3-8译码器:集成芯片74138

- 例题:

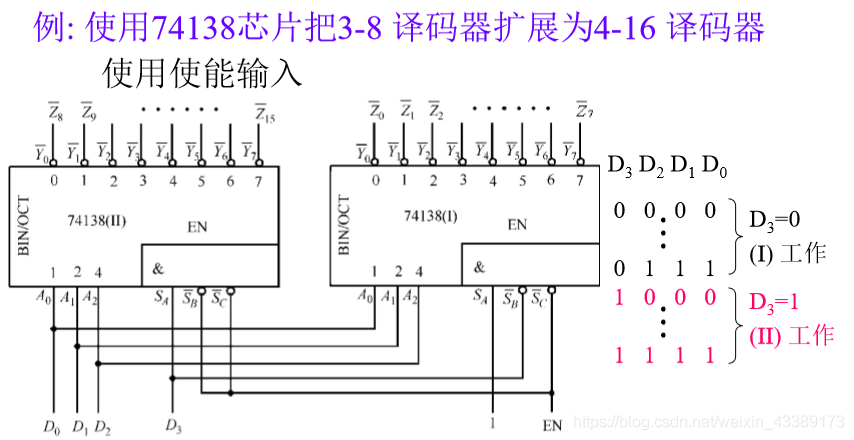

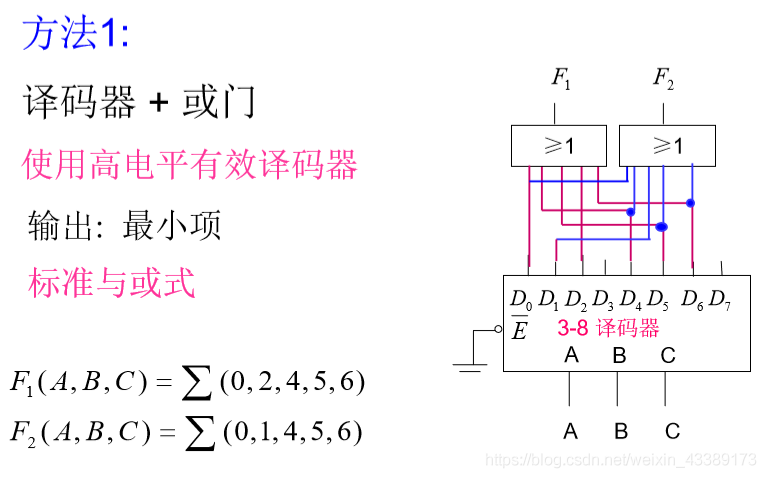

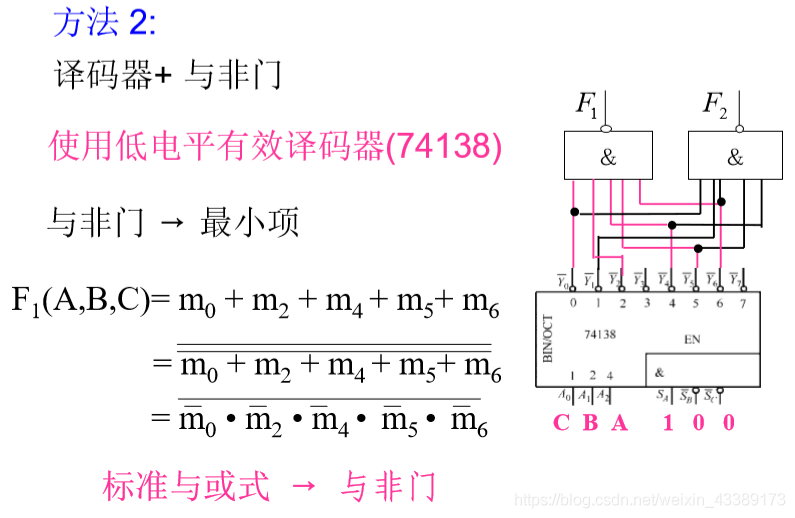

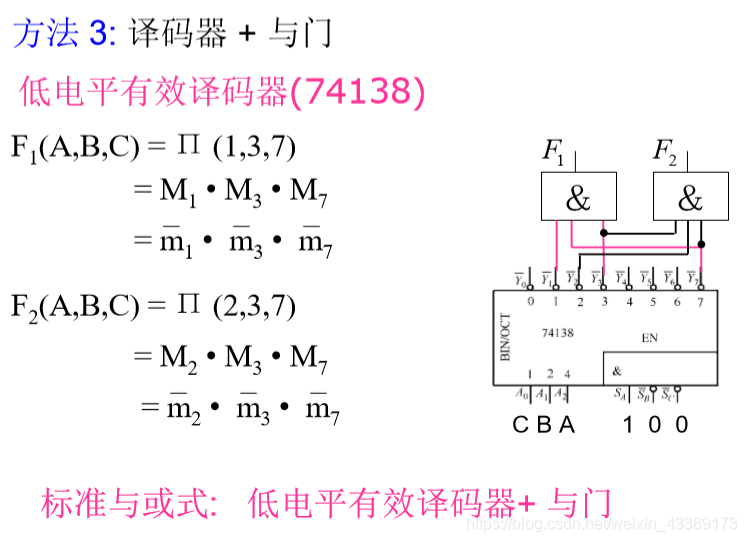

- 使用译码器实现逻辑功能

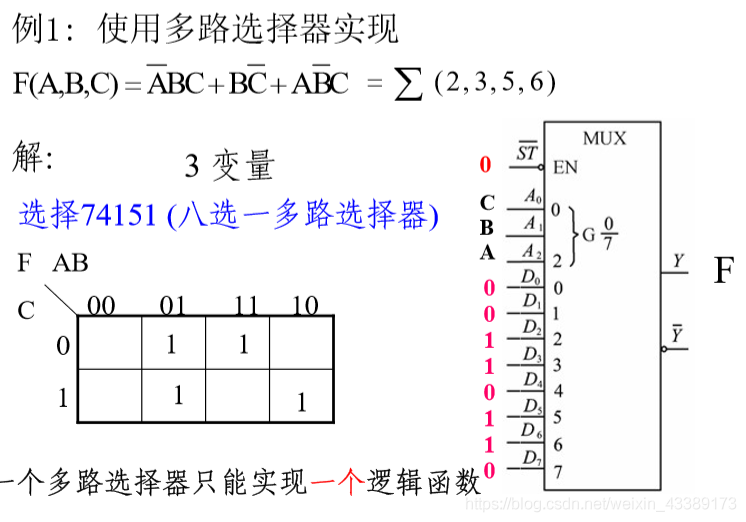

多路选择器

- 四选一多路选择器:集成芯片74153,使能端:低电平有效

- 八选一多路选择器:集成芯片74151,使能端:低电平有效

- 例题:

第五章 触发器

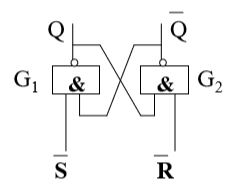

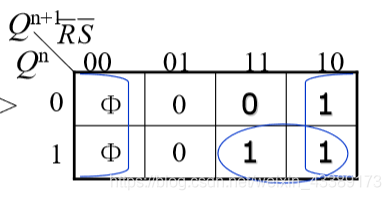

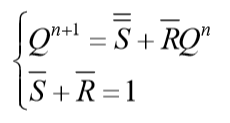

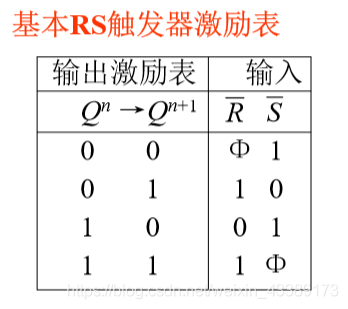

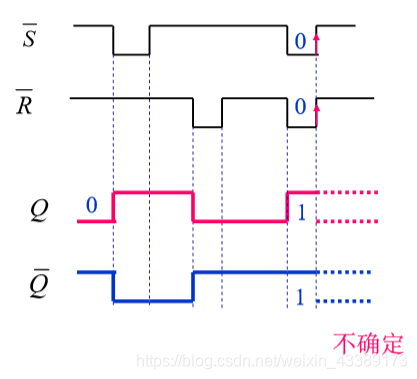

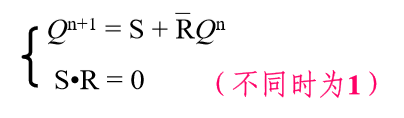

基本RS触发器

- 电路图

- 状态图

- 特征方程

- 状态转移图和激励表

- 时序图

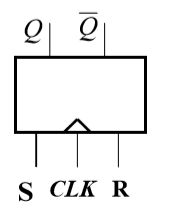

时钟触发器

- 时钟RS触发器

- 符号

- 特征方程

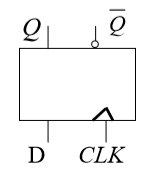

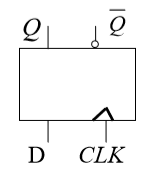

- 时钟D触发器

- 符号

- 特征方程

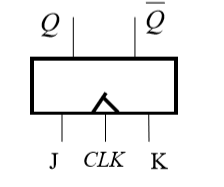

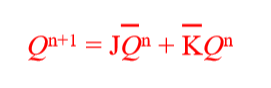

- 时钟JK触发器

- 符号

- 特征方程

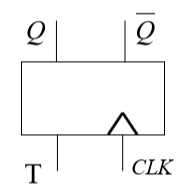

- 时钟T触发器

- 符号

- 特征方程

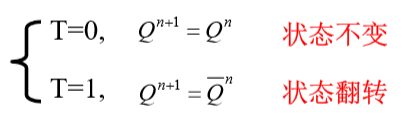

主从触发器

- 作用:克服触发器空翻

- 下边沿触发

- 符号(以JK触发器为例):

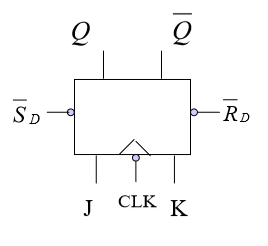

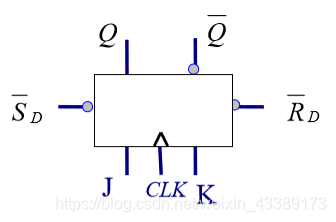

正边沿触发器

- 上边沿触发

- 符号(以JK触发器为例):

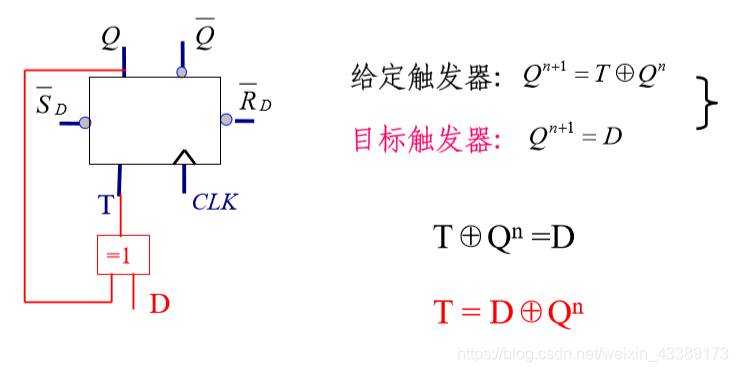

触发器间的相互转换

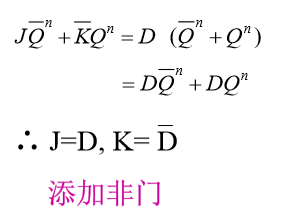

- JK触发器转换为D触发器

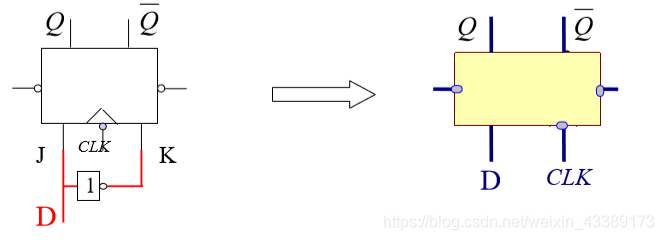

- JK触发器转换为T触发器

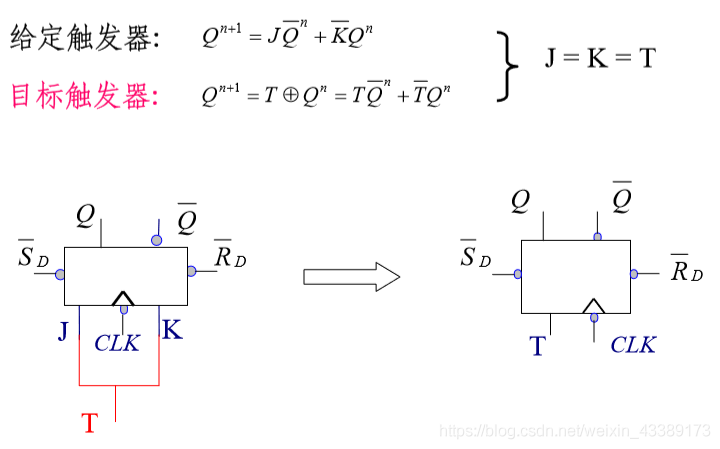

- T触发器转换为D触发器

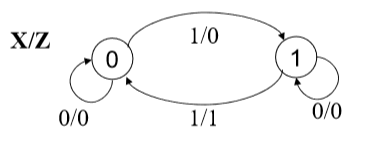

第六章 时序逻辑电路

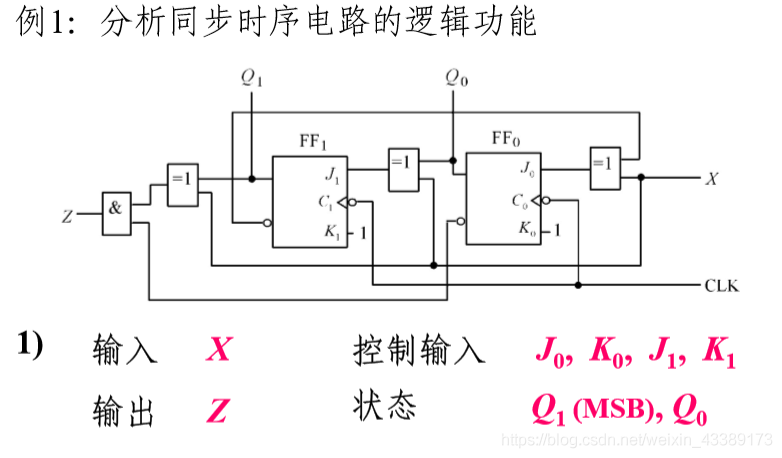

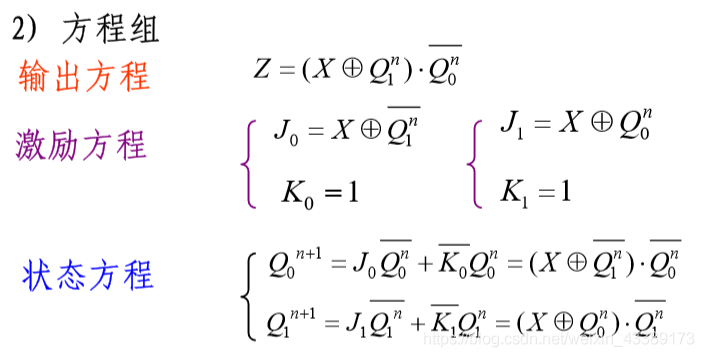

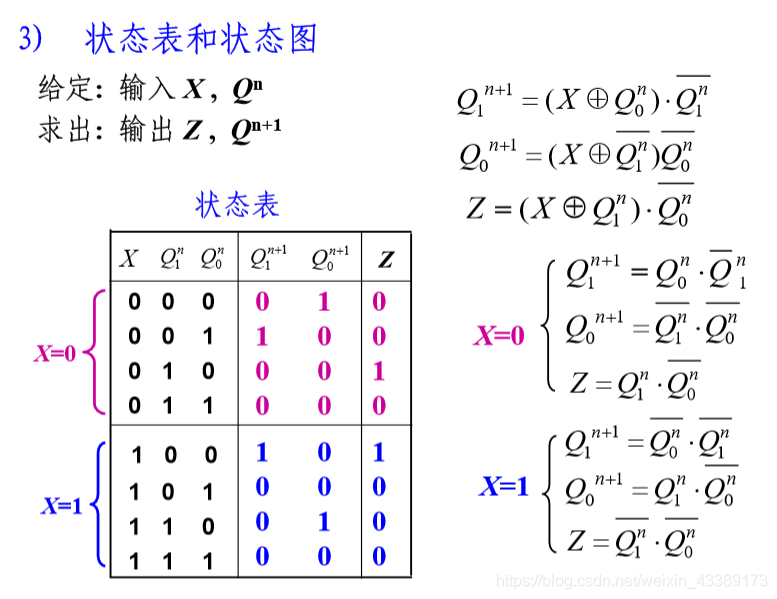

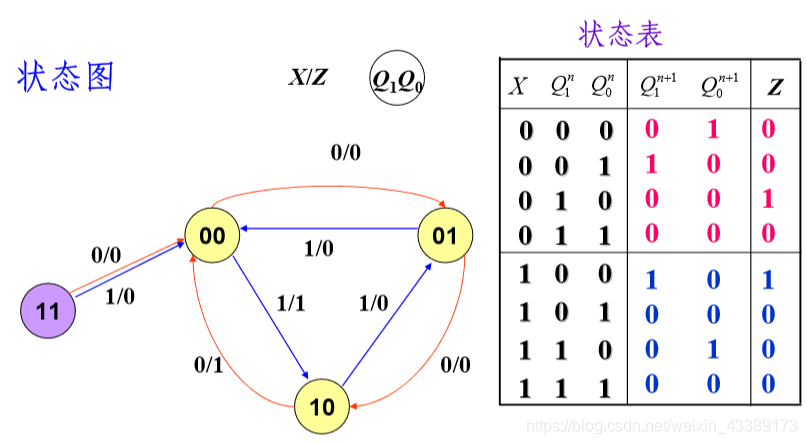

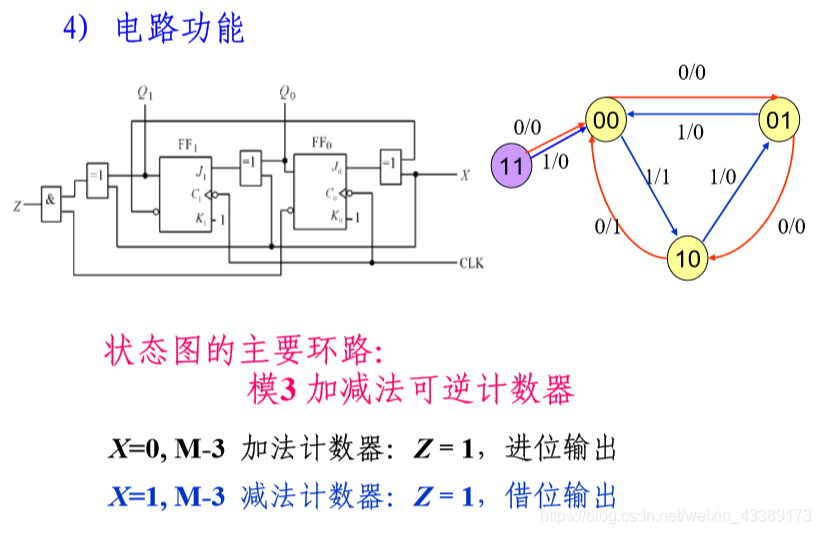

同步时序电路分析

- 写出输出方程、激励方程、状态方程

- 画出状态表和状态图

- 分析电路功能

- 例题

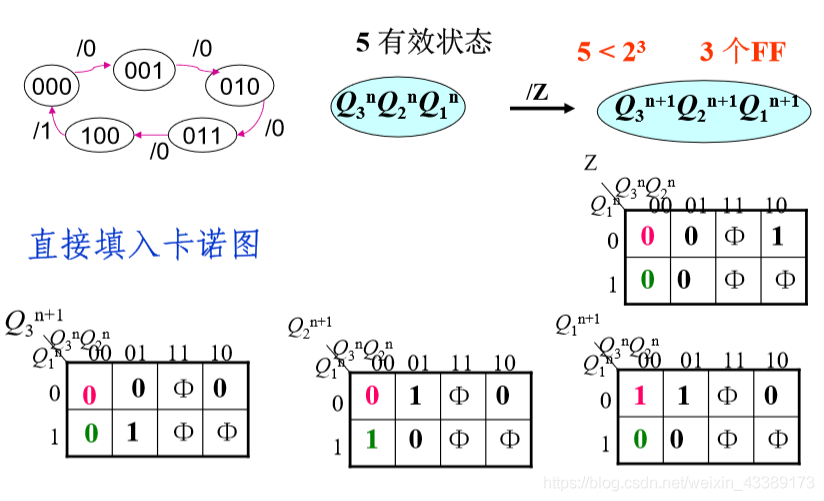

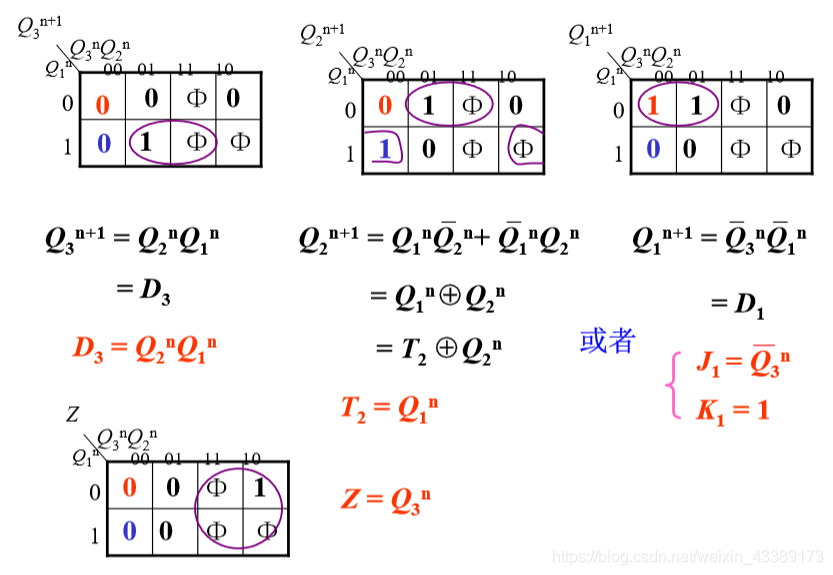

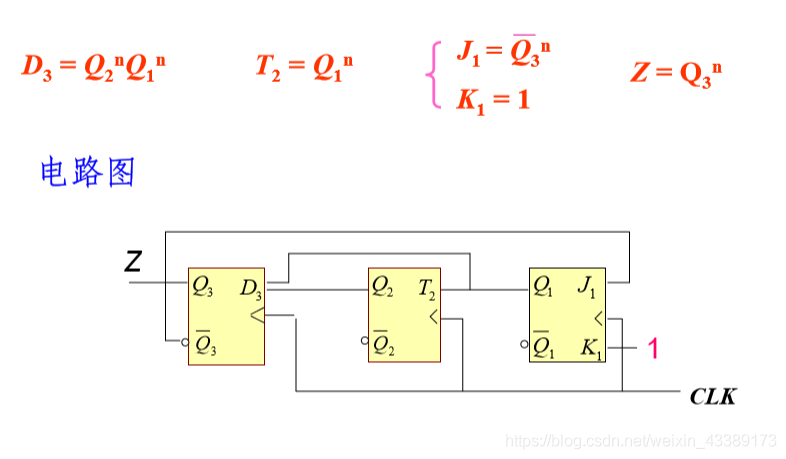

同步时序电路设计

- 画出状态转换图

- 状态化简

- 状态分配,列出状态转换编码表

- 选择触发器类型

- 求状态方程、驱动方程、输出方程

- 画电路图

- 检查电路能否自启动

- 例:设计模五计数器

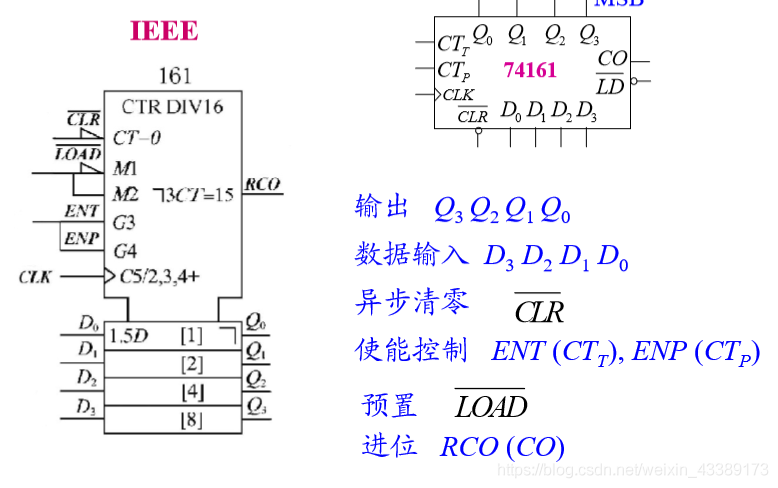

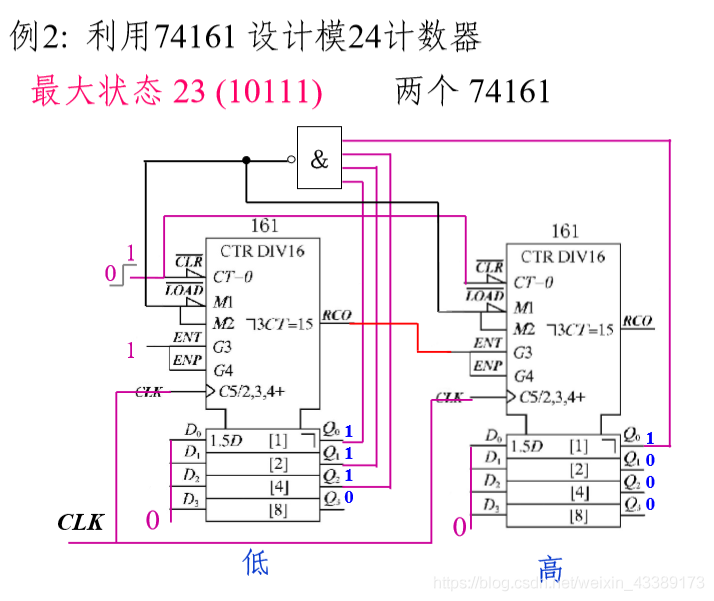

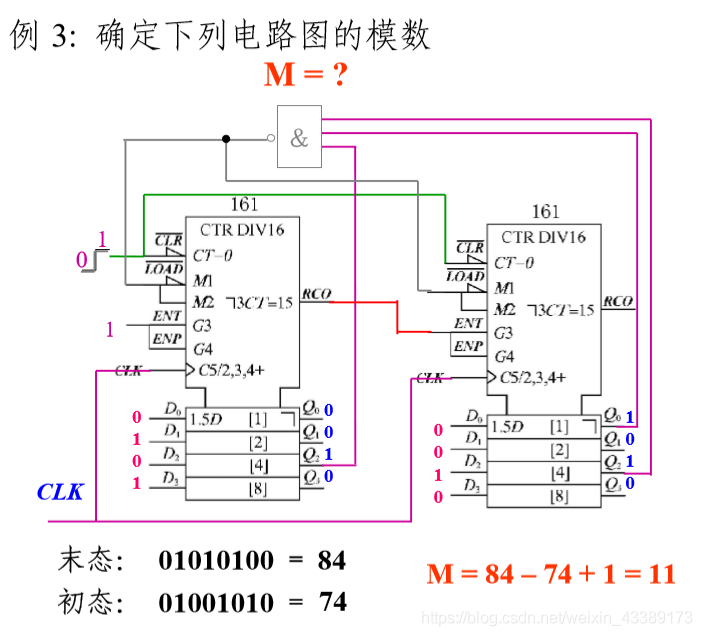

计数器(74161)

- 符号:(计数时,ENT=1;进位时,RCO=1,其他时刻,RCO=0)

- 例1

- 例2

第七章 脉冲波形的产生与变换

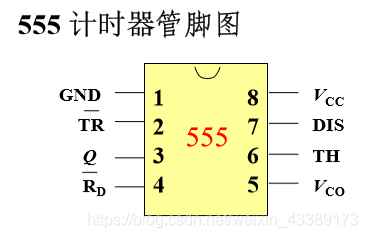

555定时器

- 管脚图

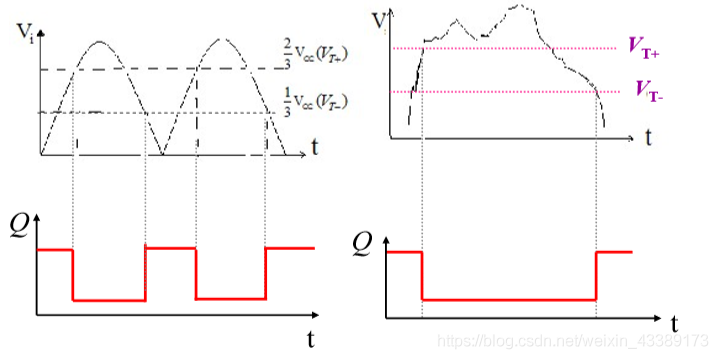

施密特触发器

- 电压特性

- 正向阈值电压Vt+=2/3Vcc

- 负向阈值电压Vt-=1/3Vcc

- 回差电压△V=(Vt+)-(Vt-)

- 波形变化

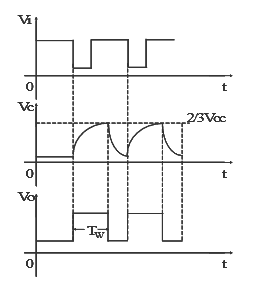

单稳态触发器

- 暂稳态持续时间Tw=1.1RC

- Vc,Vo波形图

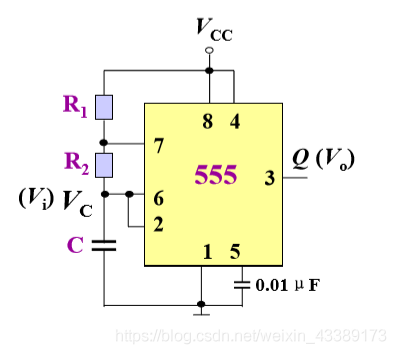

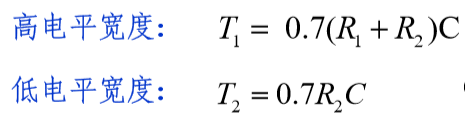

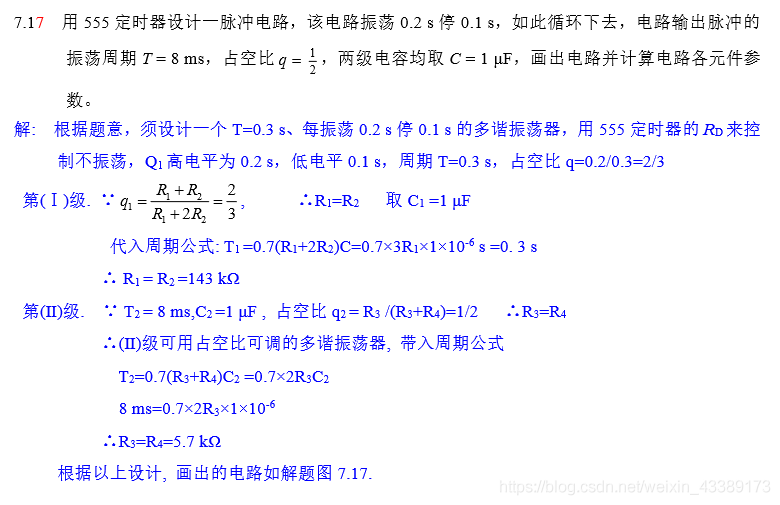

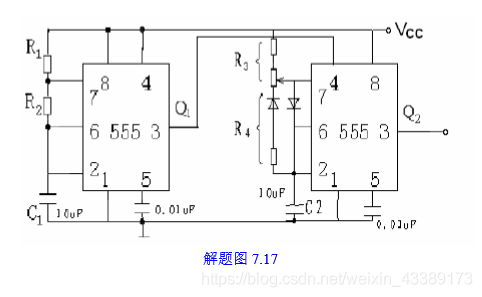

多谐振荡器

- 电路图

- 性质

- 例题

第九章 数模与模数转换

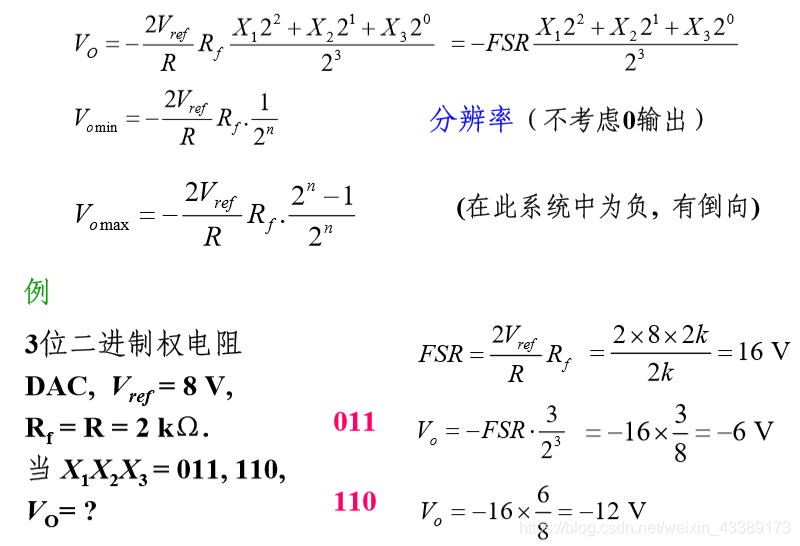

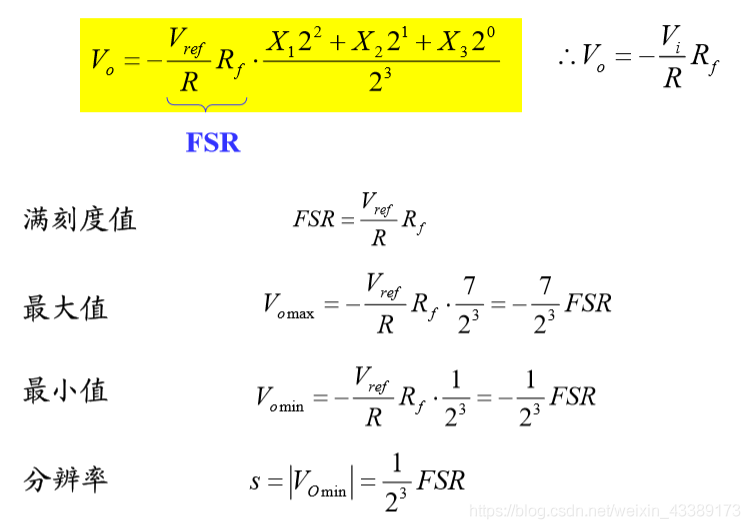

数模转换电路(DAC)

- 全电阻网络DAC

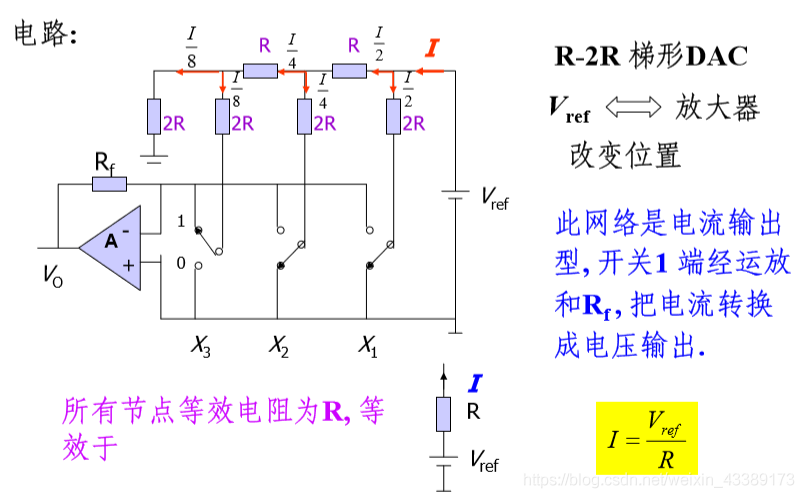

- R-2R 梯形电阻网络DAC

- R-2R 倒梯形电阻DAC

模数转换电路(ADC)

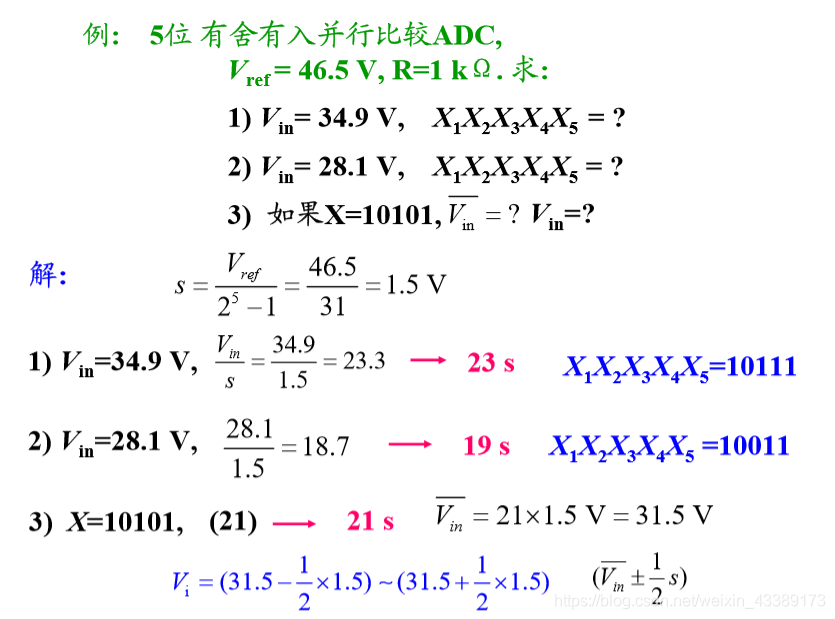

- 有舍有入并行比较

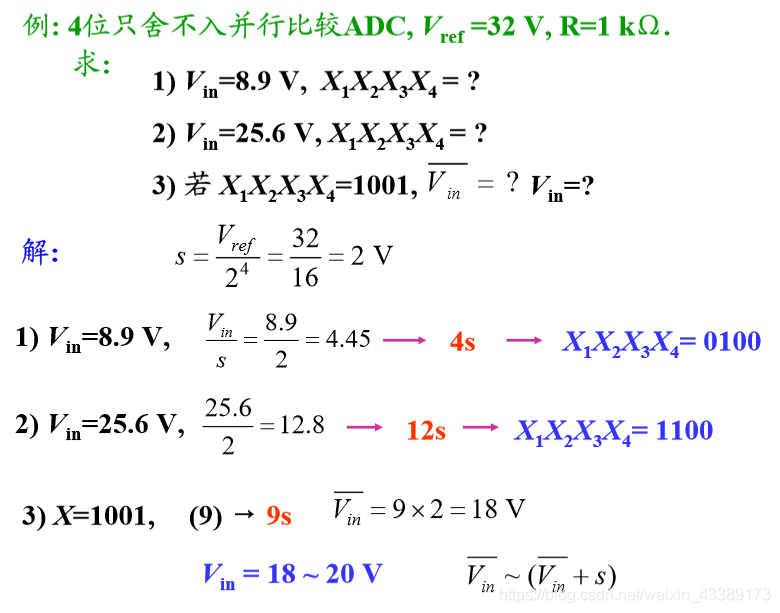

- 只舍不入并行比较

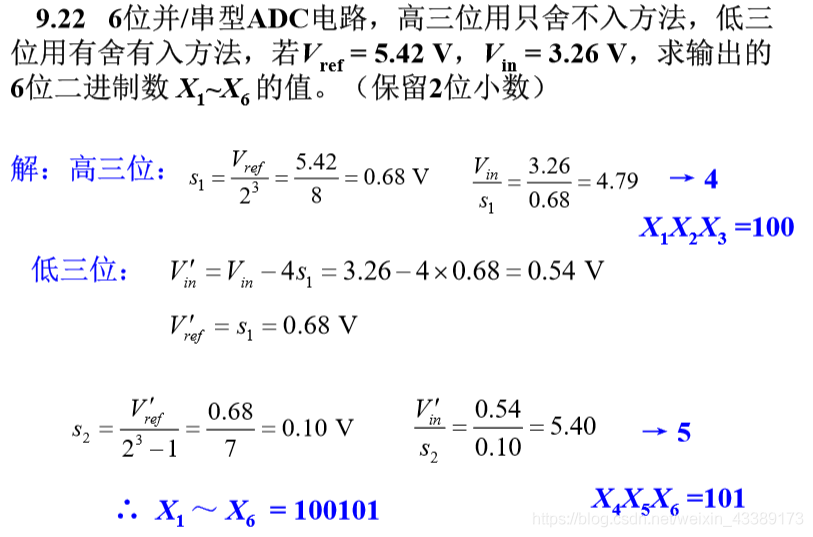

- 并/串型ADC

- 高4位只舍不入,低4位有舍有入

- 例题

第十章 半导体存储器

随机存储器(RAM)

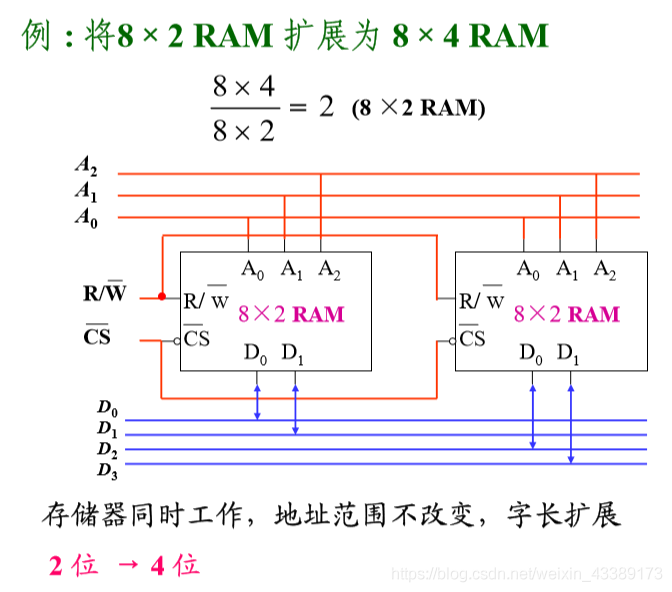

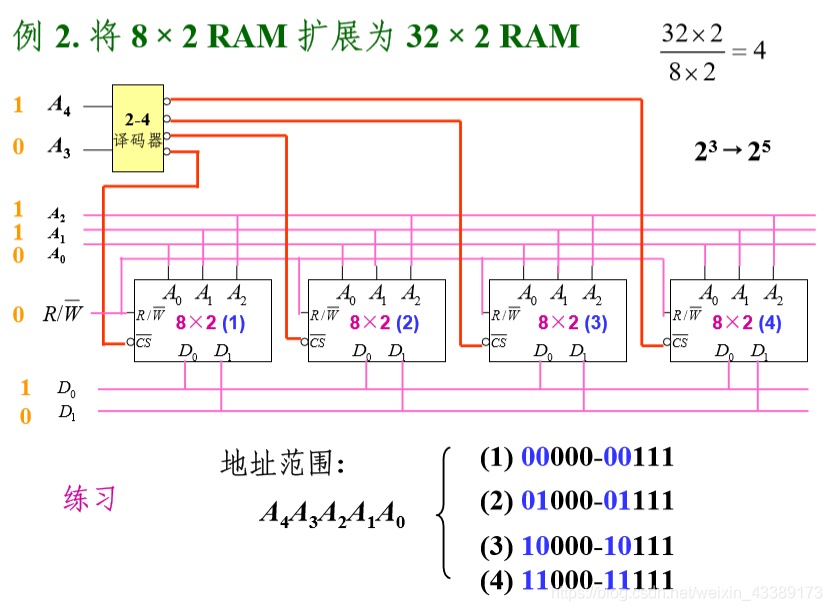

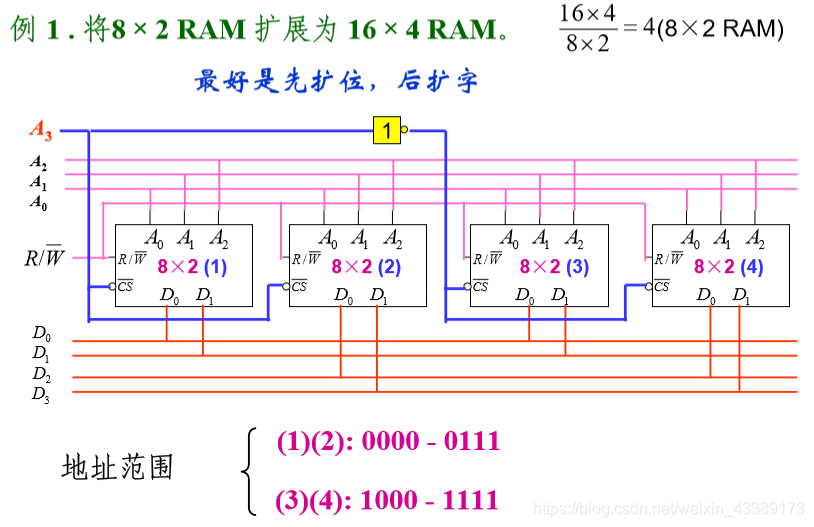

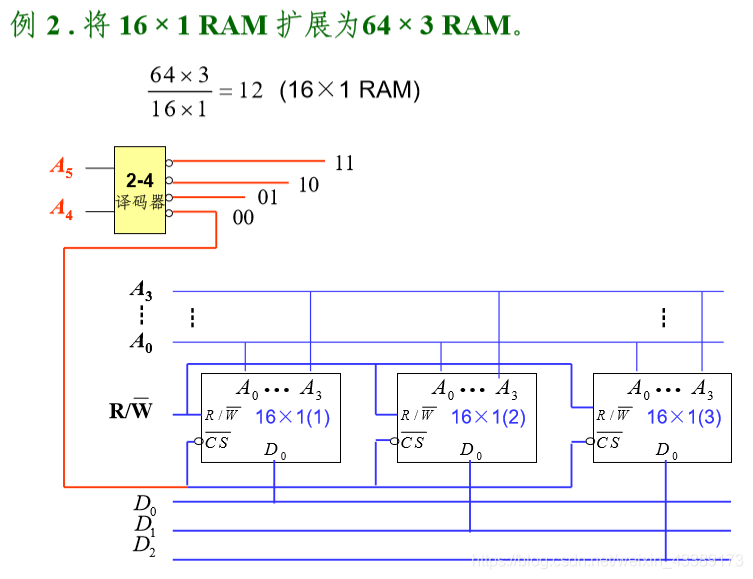

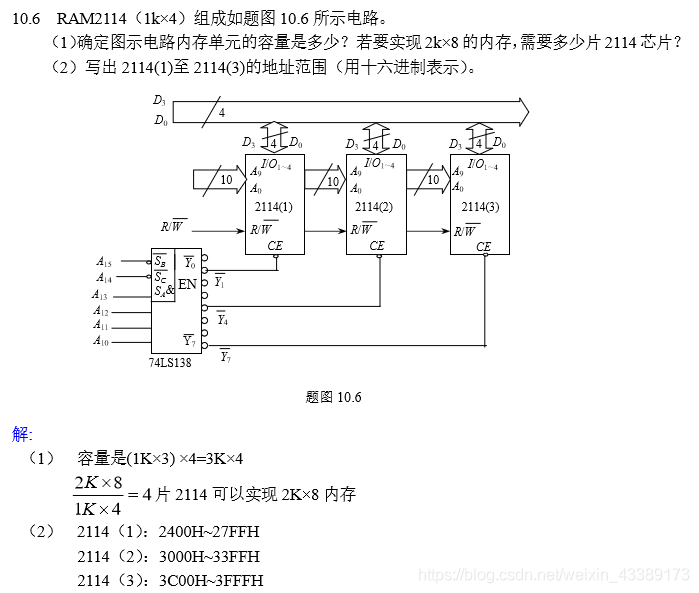

RAM扩展

- 位扩展

- 方法:相同RAM并行连接;共用:地址线,R/W,CS

- 字扩展

- 方法:增加地址线;使用CS扩展字;共用:原始地址线,R/W,数据线

- 字长和地址扩展

- 先扩位,后扩字

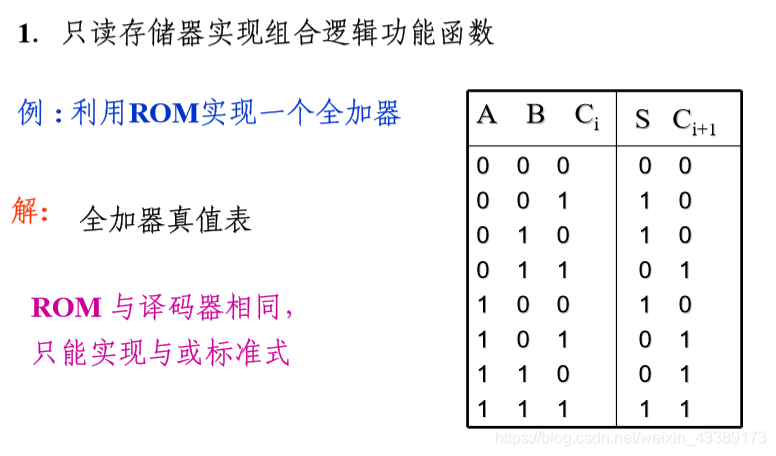

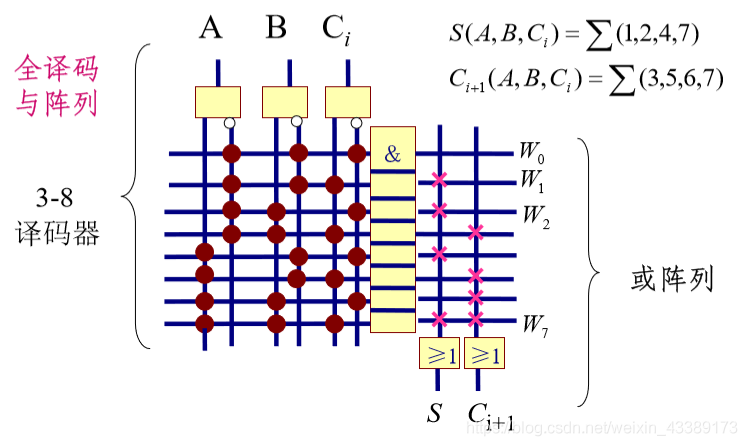

只读存储器(ROM)

- ROM存储矩阵节点连接图